As part of my effort to lean more about cpu design I wanted to make a verilog version of the DEC PDP-8/I cpu. My goal has always been to boot TSS/8.

The rtl implements an PDP-8/I in verilog with console emulation and all of the parts one would need to boot TSS/8.

It boots TSS/8 on the FPGA! After much debugging in sim everything seems to work correctly. I can run focal and basic and pald without errors and create files and read them back. I did a lot of comparison between the simulation and simh as a behavioral model.

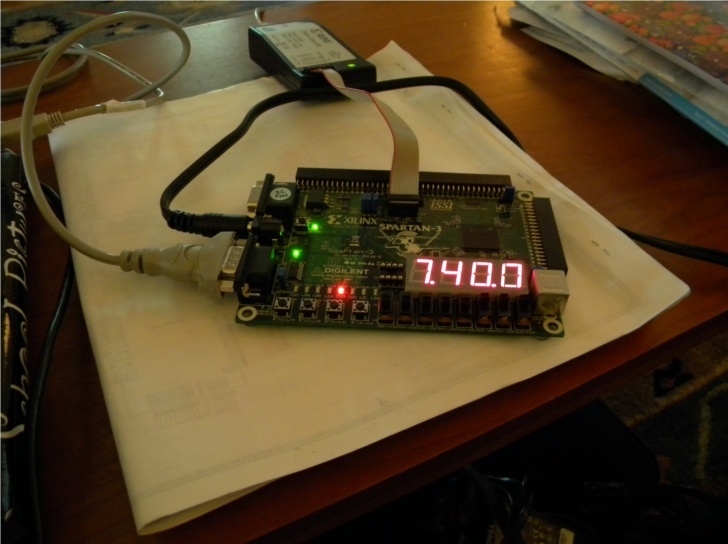

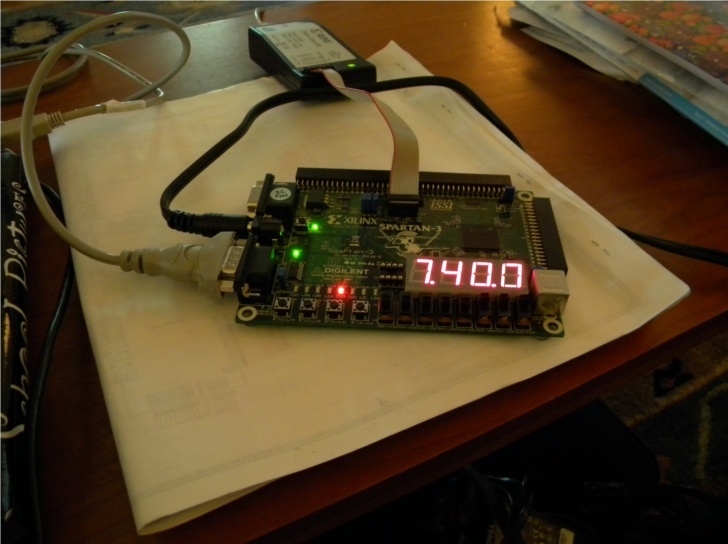

The cpu speed is selectable via the switches and the PC & AC show up on the LED's. The PC and AC are displayed on the S3's LED's. The RF08 emulator uses a stock IDE disk which connects to the S3 FPGA board with an adapter. I simply copied the file "rf.dsk" to a IDE disk using "dd" as a raw disk copy. I'm currently using an "IDE to CF" adapter and copying images onto small CF disks.

In simulation I use a "pli" module to model the ide disk. I also have a behavioral model for the RF08 which uses a disk image.

Now that I can boot TSS/8 via the serial port, I plan to turn on the verilog which creates a VT100 on a VGA display with a PS/2 keyboard. I wrote that code years ago and it could stand some review & revision...

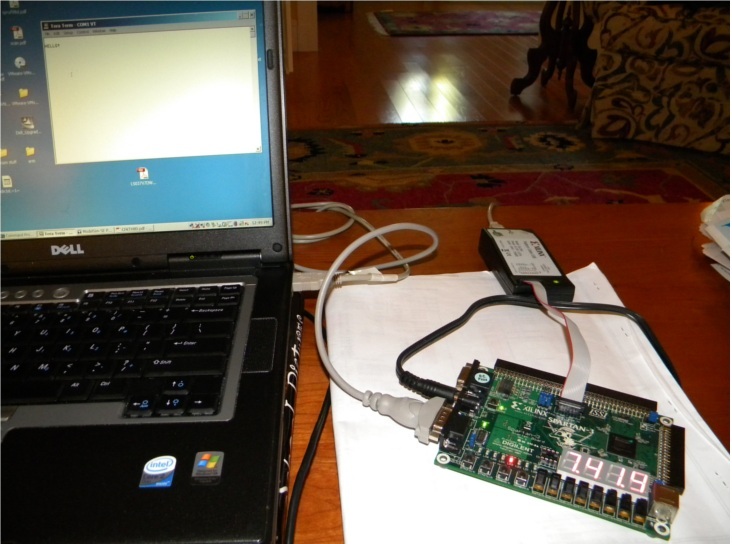

If you look closely at the picture you can see the "HELLO!" message sent by the uart test code in

rom/uart.pal. I'll put some TSS/8 boot messages soon.

Here's a silly movie of the code running the uart test. You can barely see the letters coming out on the teraterm window.

As part of this effort I have cleaned up the only machine readable source code for TSS/8 I could find. Thanks to John Wilson for typing it all in. And to Tim Radde and Vincent Slyngstad for doing most of the correction work. I did a little more cleanup to get it to match the binaries completely.

To check the source, I recompiled it with "macro8x" and compared the output bin files with the data from the RF08 disk. I made some corrections to the source to get it to compare correctly.

I then wrote a "disk maker" program which allows me to extract and insert new .bin files into an existing RF08 disk image.

Before I wrote the rtl I wrote a simple behavioral model to test my assumptions. It includes RF08 "emulation" using the disk image. I spent a lot of time comparing traces from simh with the behavioral model. I made a modified version of simh which allows me to force feed console input to make the traces more deterministic.

Once the behavioral model booted focal and tss/8 I wrote the RTL. I again compared simulation traces with simh. Once it was close I ran the extended memory and instruction diagnostics (MAINDEC). Those found a lot of subtle bugs. Once clean I added the console, rf08 and clock emulation. And did more debugging, mostly of interrupts.

The latest rtl snapshot is ready to run on hardware. I have a home made IDE adapter for the S3 board. A direct block copy of the rf disk image to the IDE is the last step.

The simulation boots TSS/8 and runs various commands. There are test benches and PLI modules for testing disk access. The rtl currently passes the instruction and extended memory diagnostics as well part of the RF08 diagnostics (it doesn't fail but I stopped the sim after one pass).

brad@mini:~/cpus/pdp8/verif$ cat yy | ../utils/ushow/ushow ... output: LOAD, DUMP, START, ETC? START MONTH-DAY-YEAR: 01:01:85 HR:MIN - 10:10 . brad@mini:~/cpus/pdp8/verif$

To run from the FPGA I made a special version of the RF08 disk controller which buffers a small block (256 words) and uses an IDE disk as a backing store. The console is run through a 9600 baud UART which connects to an RS-232 transciever. The system clock is 50MHz but can be divided down for slower operation. The PC and AC are routed to LED's on the Digilent S3 development board. The 32k by 12 ram is mapped to an external sram on the S3 board. Everying fits in a small Xilinx Spartan3 FPGA.

For my pdp-11 project I build an simple adapter which allow me to connect to an stock IDE disk drive. The RF08 controller can read and write blocks from this drive. Each 2 byte tuple of 16 bits on the drive maps to one 12 bit location on the RF08 disk; this mapping is identical to the file mapping used by simh.

There is a bug which causes the console to hang now and then. After a while it starts working again. I'm not sure while but I'll find it eventually.

I have not added a timeout flush to the RF08 write code. If there is data in the buffer but not written to the disk it won't get to the disk unless a competing read or write occurs. I'll fix this soon.

The current rtl passes the the RF08 diags, but I'm sure that means a lot. I'm not sure I have run code which tests writes (I could use a pdf of the source listing for the PDP-8 RF08 diags).

I would ignore the older versions as they are poorly written, but do contain most of the functionality. I included them just for reference.

I'll keep posting snapshots as I make progress. The snap shots contain everything needed to reproduce the simulations and boot TSS/8, as well as run the diagnostics. The regression tests are not completely automated yet, but plan to do that.

Current snapshot:

Historial releases: