# Intel<sup>®</sup> StrongARM<sup>\*</sup> SA-1111 Microprocessor Companion Chip

**Developer's Manual**

**July 2000**

Order No: 278242-003

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SA-1111 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 7/19/00

\*Other brands and names are the property of their respective owners.

# intel... Contents

| 1 | Intro | duction   | 1                                                        | 1–1  |

|---|-------|-----------|----------------------------------------------------------|------|

|   | 1.1   | Conver    | ntions                                                   | 1–1  |

|   |       | 1.1.1     | Specifying Bit and Signal Values                         |      |

|   |       | 1.1.2     | Representing Numbers                                     |      |

|   |       | 1.1.3     | Register Names                                           |      |

|   |       | 1.1.4     | Bits in Register Descriptions                            |      |

|   | 1.2   |           | Documentation                                            |      |

|   | 1.3   |           | n Block Diagram                                          |      |

|   | 1.4   |           | Descriptions                                             |      |

| 2 |       | •         | Description                                              |      |

| _ | 2.1   |           | onal Blocks                                              |      |

|   | ۷.۱   | 2.1.1     | System Bus Interface (SBI)                               |      |

|   |       | 2.1.1     |                                                          |      |

|   | 2.2   |           | Intel® StrongARM* SA-1111 Subsystems                     |      |

|   | 2.2   |           | Generation and Distribution                              |      |

|   | 2.3   |           | Reset                                                    |      |

|   | 2.4   |           | of Operations                                            |      |

|   |       | 2.4.1     | Normal Mode                                              |      |

|   |       | 2.4.2     | Doze Mode                                                |      |

|   | 0.5   | 2.4.3     | Sleep Mode                                               |      |

|   | 2.5   | l est     |                                                          | 2–11 |

| 3 | Syst  | em Bus    | Interface (SBI)                                          | 3–1  |

|   | 3.1   | Signal    | Description                                              | 3–1  |

|   |       | 3.1.1     | Intel® StrongARM* SA-1110 System Bus Interface - Signals | 3–1  |

|   |       | 3.1.2     | System Bus Interface (SBI) - Internal Buses and Signals  | 3–2  |

|   |       | 3.1.3     | Other Internal Interface Signals                         |      |

|   | 3.2   | Functio   | onal Description                                         | 3–4  |

|   |       | 3.2.1     | Register Accesses and the Register Access Bus (RAB)      |      |

|   |       | 3.2.2     | PCMCIA and CF Access                                     |      |

|   |       | 3.2.3     | DMA Access to System Memory                              |      |

|   |       |           | 3.2.3.1 Acquiring Internal and External System Buses     |      |

|   |       |           | 3.2.3.2 DMA Bus Arbitration                              |      |

|   |       |           | 3.2.3.3 Shared Memory Controller (SMC)                   |      |

|   |       |           | 3.2.3.4 DRAM Address Generation                          |      |

|   |       |           | 3.2.3.5 DRAM Control Signal Generation                   | 3–12 |

|   | 3.3   | SBI Re    | gistersgisters                                           | 3–15 |

|   |       | 3.3.1     | Control Register (SKCR)                                  | 3–15 |

|   |       | 3.3.2     | Shared Memory Controller Register (SMCR)                 | 3–16 |

|   |       | 3.3.3     | ID Register (SKID)                                       | 3–18 |

|   |       | 3.3.4     | Memory Map                                               | 3–18 |

| 4 | SA-1  | 1111 Into | ernal Bus Architecture                                   | 4–1  |

|   | 4.1   | Reaiste   | er Access Bus                                            | 4–1  |

|   | •••   | 4.1.1     | RAB Central Address Decoder                              |      |

|   |       | 4.1.2     | Signal Description                                       |      |

|   |       | 4.1.3     | RAB Cycles                                               |      |

|   |       |           | PAR Protocol                                             | 1_1  |

# int<sub>e</sub>l®

|   | 4.2                         | DMA B                                                                                                                   | us                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4–4                                                                 |

|---|-----------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

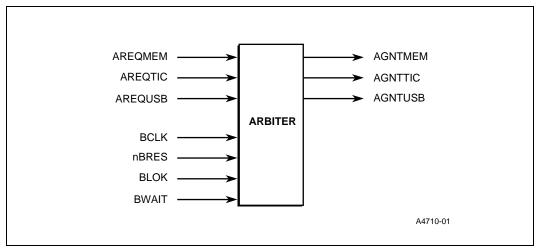

|   |                             | 4.2.1                                                                                                                   | DMA Bus Arbiter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |

|   |                             |                                                                                                                         | 4.2.1.1 DMA Arbiter Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4–5                                                                 |

|   |                             |                                                                                                                         | 4.2.1.2 Arbiter Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4–5                                                                 |

|   |                             |                                                                                                                         | 4.2.1.3 Arbiter Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4–6                                                                 |

|   |                             |                                                                                                                         | 4.2.1.4 Arbiter Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4–6                                                                 |

|   |                             | 4.2.2                                                                                                                   | DMA Bus Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4–7                                                                 |

|   |                             | 4.2.3                                                                                                                   | DMA Bus Protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                     |

| 5 | Syst                        | em Con                                                                                                                  | ntroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5–1                                                                 |

|   | 5.1                         | Functio                                                                                                                 | onal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5–1                                                                 |

|   |                             | 5.1.1                                                                                                                   | System Power Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |

|   |                             | 5.1.2                                                                                                                   | PWM Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |

|   | 5.2                         | _                                                                                                                       | mmer's Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |

|   | 0.2                         | 5.2.1                                                                                                                   | Power Control Register (SKPCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |

|   |                             | 5.2.2                                                                                                                   | Clock Divider Register (SKCDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |

|   |                             | 5.2.3                                                                                                                   | Audio Clock Divider Register (SKAUD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |

|   |                             | 5.2.4                                                                                                                   | PS/2 Mouse Clock Divider Register (SKPMC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |

|   |                             | 5.2.4                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |

|   |                             |                                                                                                                         | PS/2 Track Pad Clock Divider Register (SKPTC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                     |

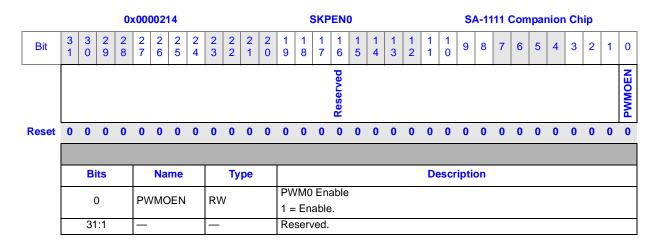

|   |                             | 5.2.6                                                                                                                   | PWM0 Enable Register (SKPEN0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                     |

|   |                             | 5.2.7                                                                                                                   | PWM0 Clock Register (SKPWM0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |

|   |                             | 5.2.8                                                                                                                   | PWM1 Enable Register (SKPEN1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                     |

|   |                             | 5.2.9                                                                                                                   | PWM1 Clock Register (SKPWM1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |

|   |                             | 5.2.10                                                                                                                  | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5–8                                                                 |

| 6 | USB                         | Host In                                                                                                                 | terface Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6–1                                                                 |

|   | 6.1                         | Functio                                                                                                                 | onal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6–1                                                                 |

|   |                             | 6.1.1                                                                                                                   | USB Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6–1                                                                 |

|   |                             | 0.1.1                                                                                                                   | 005 (0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • .                                                                 |

|   |                             | 6.1.1                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |

|   |                             | •                                                                                                                       | USB Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6–1                                                                 |

|   |                             | 6.1.2                                                                                                                   | USB Suspend Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6–1<br>6–2                                                          |

|   |                             | 6.1.2                                                                                                                   | USB Suspend  Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6–1<br>6–2<br>6–2<br>6–2                                            |

|   |                             | 6.1.2                                                                                                                   | USB Suspend  Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6–1<br>6–2<br>6–2<br>6–2                                            |

|   |                             | 6.1.2                                                                                                                   | USB Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6–1<br>6–2<br>6–2<br>6–3                                            |

|   |                             | 6.1.2<br>6.1.3                                                                                                          | USB Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6–1<br>6–2<br>6–2<br>6–3<br>6–4                                     |

|   |                             | 6.1.2<br>6.1.3                                                                                                          | USB Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6–1<br>6–2<br>6–2<br>6–3<br>6–4<br>6–4                              |

|   |                             | 6.1.2<br>6.1.3                                                                                                          | USB Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6–1<br>6–2<br>6–2<br>6–3<br>6–4<br>6–4                              |

|   |                             | 6.1.2<br>6.1.3                                                                                                          | USB Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6–1<br>6–2<br>6–2<br>6–3<br>6–4<br>6–4<br>6–4                       |

|   | 6.2                         | 6.1.2<br>6.1.3                                                                                                          | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6–1<br>6–2<br>6–2<br>6–3<br>6–4<br>6–4<br>6–4<br>6–5                |

|   | 6.2                         | 6.1.2<br>6.1.3                                                                                                          | USB Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-2<br>6-2<br>6-3<br>6-4<br>6-4<br>6-4<br>6-5<br>6-5         |

|   | 6.2                         | 6.1.2<br>6.1.3<br>6.1.4                                                                                                 | USB Suspend  Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6–1<br>6–2<br>6–2<br>6–3<br>6–4<br>6–4<br>6–4<br>6–5<br>6–5         |

|   | 6.2                         | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1                                                                              | USB Suspend Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6–1<br>6–2<br>6–2<br>6–3<br>6–4<br>6–4<br>6–5<br>6–5<br>6–5         |

|   | 6.2                         | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1<br>6.2.2                                                                     | USB Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-1 6-2 6-2 6-2 6-3 6-4 6-4 6-4 6-5 6-5 6-5                         |

|   |                             | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                   | USB Suspend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-1 6-2 6-2 6-2 6-3 6-4 6-4 6-4 6-5 6-5 6-6 6-6                     |

|   | 6.2                         | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                   | USB Suspend Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-1 6-2 6-2 6-2 6-3 6-4 6-4 6-5 6-5 6-5 6-6 6-6 6-6 6-6             |

|   |                             | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Program<br>6.3.1                               | USB Suspend Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-1 6-2 6-2 6-2 6-3 6-4 6-4 6-5 6-5 6-5 6-6 6-6 6-7 6-7             |

|   |                             | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Prograi<br>6.3.1<br>6.3.2                      | USB Suspend Power Management 6.1.3.1 USB Clock Stopping and Power Enable 6.1.3.2 Port Resume Interrupt 6.1.3.3 Summary of Low Power Operation Suggested Power-Management Routines 6.1.4.1 Initial Port Power-Down Sequence 6.1.4.2 Low-Power Mode in Suspend State Sequence 6.1.4.3 Low-Power Mode after Device Disconnect Sequence 6.1.4.4 Disable USB Port lock Interfaces  External Pin Interface Internal RAB Bus Interface Internal DMA Bus Interface Interrupt Generation  mmer's Model Status Register Interrupt Test Register                                         | 6-1 6-2 6-2 6-2 6-3 6-4 6-4 6-5 6-5 6-5 6-6 6-7 6-9                 |

|   | 6.3                         | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Prograi<br>6.3.1<br>6.3.2<br>6.3.3             | USB Suspend Power Management 6.1.3.1 USB Clock Stopping and Power Enable 6.1.3.2 Port Resume Interrupt 6.1.3.3 Summary of Low Power Operation Suggested Power-Management Routines 6.1.4.1 Initial Port Power-Down Sequence 6.1.4.2 Low-Power Mode in Suspend State Sequence 6.1.4.3 Low-Power Mode after Device Disconnect Sequence 6.1.4.4 Disable USB Port lock Interfaces External Pin Interface Internal RAB Bus Interface Internal DMA Bus Interface Interrupt Generation mmer's Model Status Register Interrupt Test Register Reset Register                            | 6-1 6-2 6-2 6-2 6-3 6-4 6-4 6-4 6-5 6-5 6-5 6-6 6-6 6-7 6-7 6-9 6-9 |

|   | 6.3                         | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Program<br>6.3.1<br>6.3.2<br>6.3.3<br>Registe  | USB Suspend Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-1 6-2 6-2 6-2 6-3 6-4 6-4 6-5 6-5 6-5 6-6 6-7 6-9 6-9 6-11        |

| 7 | 6.3                         | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Program<br>6.3.1<br>6.3.2<br>6.3.3<br>Registe  | USB Suspend Power Management 6.1.3.1 USB Clock Stopping and Power Enable 6.1.3.2 Port Resume Interrupt 6.1.3.3 Summary of Low Power Operation Suggested Power-Management Routines 6.1.4.1 Initial Port Power-Down Sequence 6.1.4.2 Low-Power Mode in Suspend State Sequence 6.1.4.3 Low-Power Mode after Device Disconnect Sequence 6.1.4.4 Disable USB Port lock Interfaces External Pin Interface Internal RAB Bus Interface Internal DMA Bus Interface Interrupt Generation mmer's Model Status Register Interrupt Test Register Reset Register                            | 6-1 6-2 6-2 6-2 6-3 6-4 6-4 6-5 6-5 6-5 6-6 6-7 6-9 6-9 6-11        |

| 7 | 6.3                         | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Program<br>6.3.1<br>6.3.2<br>6.3.3<br>Register | USB Suspend Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-1 6-2 6-2 6-2 6-3 6-4 6-4 6-4 6-5 6-5 6-6 6-7 6-9 6-9 6-11        |

| 7 | 6.3<br>6.4<br><b>Seri</b> a | 6.1.2<br>6.1.3<br>6.1.4<br>USB BI<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Program<br>6.3.1<br>6.3.2<br>6.3.3<br>Register | USB Suspend Power Management 6.1.3.1 USB Clock Stopping and Power Enable 6.1.3.2 Port Resume Interrupt. 6.1.3.3 Summary of Low Power Operation Suggested Power-Management Routines 6.1.4.1 Initial Port Power-Down Sequence 6.1.4.2 Low-Power Mode in Suspend State Sequence 6.1.4.3 Low-Power Mode after Device Disconnect Sequence 6.1.4.4 Disable USB Port lock Interfaces External Pin Interface Internal RAB Bus Interface Internal DMA Bus Interface Interrupt Generation mmer's Model Status Register Interrupt Test Register Reset Register er Memory Map  Controller | 6-1 6-2 6-2 6-2 6-3 6-4 6-4 6-5 6-5 6-5 6-6 6-7 6-9 6-9 7-1         |

# int<sub>el®</sub>

|   |       | 7.1.2          | Internal Interfaces                                        | 7–3  |

|---|-------|----------------|------------------------------------------------------------|------|

|   |       |                | 7.1.2.1 Register Access Bus (RAB)                          | 7–3  |

|   |       |                | 7.1.2.2 DMA Bus Interface                                  | 7–3  |

|   |       |                | 7.1.2.3 Other Signals                                      |      |

|   | 7.2   | Serial A       | Audio Controller Operation                                 | 7–4  |

|   |       | 7.2.1          | RAB Bus Data Transfers                                     |      |

|   |       | 7.2.2          | DMA Audio Data Transfers                                   | 7–5  |

|   |       | 7.2.3          | Serial Audio Clocks and Sampling Frequencies               |      |

|   | 7.3   |                | ormats                                                     |      |

|   |       | 7.3.1          | Parallel Data Formats: Buffer and DRAM Storage             |      |

|   |       | 7.3.2          | Serial Data Formats for Transfer to/from Codecs            |      |

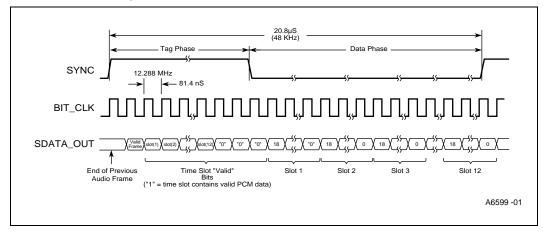

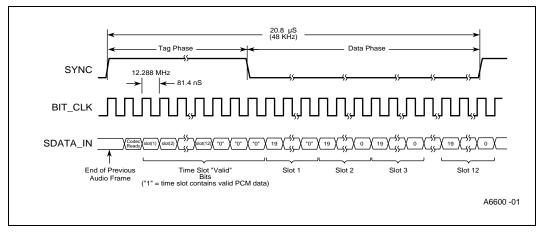

|   |       |                | 7.3.2.1 AC-link Serial Data                                |      |

|   |       |                | 7.3.2.2 I2S and MSB-Justified Serial Audio Formats         |      |

|   | 7.4   | Serial A       | Audio Controller Registers                                 |      |

|   |       | 7.4.1          | Serial Audio Control Registers                             |      |

|   |       | 7.7.1          | 7.4.1.1 Serial Audio Common Control Register (SACR0)       |      |

|   |       |                | 7.4.1.2 Serial Audio Alternate Mode (I2S/MSB-Justified)    | 7 5  |

|   |       |                | Control Register (SACR1)                                   | 7–10 |

|   |       |                | 7.4.1.3 Serial Audio AC-link Control Register (SACR2)      | 7–12 |

|   |       | 7.4.2          | Serial Audio Status Register (SASR0)                       |      |

|   |       | 7.4.3          | Serial Audio Status Registers (SASR1)                      |      |

|   |       | 7.4.4          | Serial Audio Status Clear Register (SASCR)                 |      |

|   |       | 7.4.5          | L3 Control Bus Address Register (L3CAR)                    |      |

|   |       | 7.4.6          | L3 Control Bus Data Register (L3CDR)                       |      |

|   |       | 7.4.7          | AC-link Control Registers                                  |      |

|   |       | 7.4.7<br>7.4.8 | AC-link Command Address Register (ACCAR)                   |      |

|   |       | _              |                                                            |      |

|   |       | 7.4.9          | AC-link Command Data Register (ACCDR)                      |      |

|   |       | 7.4.10         | AC-link Status Address Register (ACSAR)                    |      |

|   |       | 7.4.11         | AC-link Status Address Register (ACSDR)                    |      |

|   |       |                | Serial Audio DMA Transmit Control/Status Register (SADTCS) | 7–21 |

|   |       | 7.4.13         | Serial Audio DMA Transmit Buffer Start Address             |      |

|   |       |                | Register A (SADTSA)                                        |      |

|   |       |                | Serial Audio DMA Transmit Buffer Count Register A (SADTCA) | 7–23 |

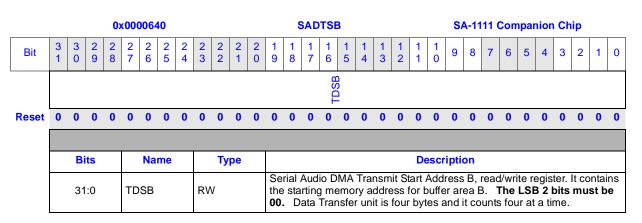

|   |       | 7.4.15         | Serial Audio DMA Transmit Buffer Start Address             |      |

|   |       |                | Register B (SADTSB)                                        |      |

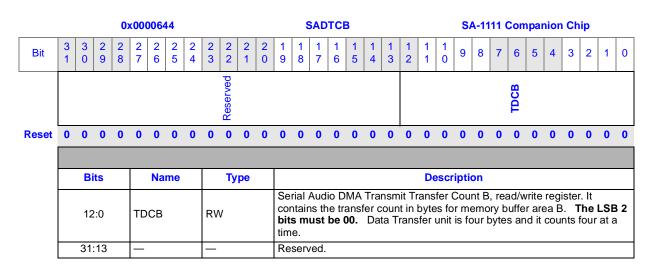

|   |       |                | Serial Audio DMA Transmit Buffer Count Register B (SADTCB) |      |

|   |       |                | Serial Audio DMA Receive Control/Status Register (SADRCS)  | 7–24 |

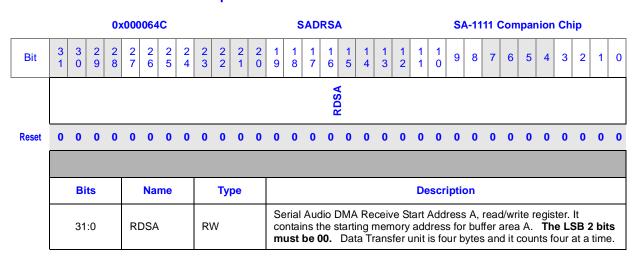

|   |       | 7.4.18         | Serial Audio DMA Receive Buffer Start Address              |      |

|   |       |                | Register A (SADRSA)                                        |      |

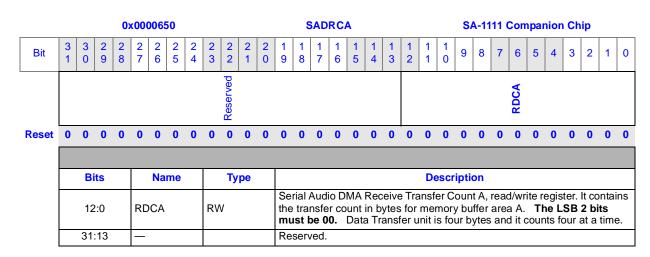

|   |       |                | Serial Audio DMA Receive Buffer Count Register A (SADRCA)  | 7–26 |

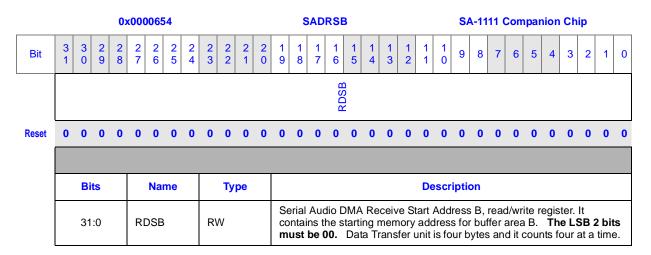

|   |       | 7.4.20         | Serial Audio DMA Receive Buffer Start Address              |      |

|   |       |                | Register B (SADRSB)                                        |      |

|   |       | 7.4.21         | Serial Audio DMA Receive Buffer Count Register B (SADRCB)  |      |

|   |       |                | Serial Audio Interrupt Test Register (SAITR)               |      |

|   |       |                | Serial Audio Data Register (SADR)                          |      |

|   |       | 7.4.24         | Serial Audio Controller: Register Memory Map               | 7–29 |

| 8 | SSP S | Serial F       | Port                                                       | 8–1  |

|   | 8.1   | Signal I       | Description                                                | 8–1  |

|   | J.,   | 8.1.1          | External Interface to SSP, SPI, or Microwire Peripherals   |      |

|   |       | 8.1.2          | Internal Interfaces                                        |      |

|   |       | 5.1.2          | 8.1.2.1 Register Access Bus (RAB)                          |      |

|   |       |                | U.T.Z. I Tregister Access Dus (TAD)                        | 2    |

# intel

|   |      |          | 8.1.2.2 Data Block Transfers                                | 8–2  |

|---|------|----------|-------------------------------------------------------------|------|

|   | 8.2  | SSP O    | peration                                                    |      |

|   |      | 8.2.1    | Processor-Initiated Data Transfer                           |      |

|   | 8.3  | Data F   | ormats                                                      | 8–3  |

|   |      | 8.3.1    | Serial Data Formats for Transfer to/from Peripherals        | 8–3  |

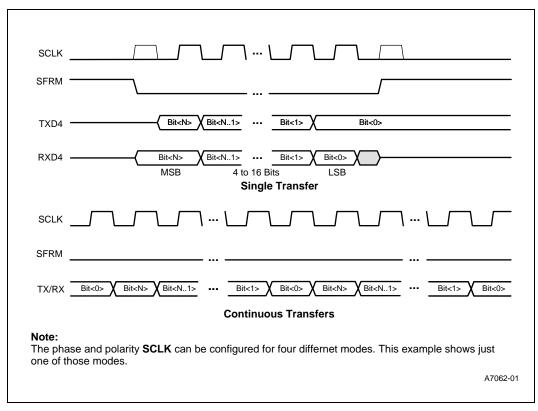

|   |      |          | 8.3.1.1 SSP Format - Detail                                 | 8–4  |

|   |      |          | 8.3.1.2 SPI Format - Detail                                 |      |

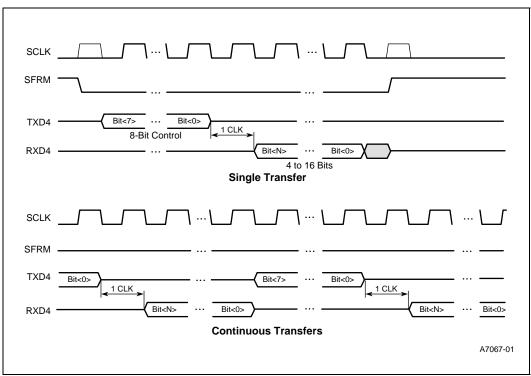

|   |      |          | 8.3.1.3 Microwire* Format - details                         | 8–5  |

|   |      | 8.3.2    | Parallel Data Formats for Buffer Storage                    | 8–6  |

|   | 8.4  | Buffer ( | Operation                                                   | 8–6  |

|   | 8.5  |          | Rate Generation                                             |      |

|   | 8.6  | SSP S    | erial Port Registers                                        | 8–7  |

|   |      | 8.6.1    | SSP Control Register 0                                      | 8–7  |

|   |      |          | 8.6.1.1 Data Size Select (DSS)                              |      |

|   |      |          | 8.6.1.2 Frame Format (FRF)                                  | 8–8  |

|   |      |          | 8.6.1.3 Synchronous Serial Port Enable (SSE)                |      |

|   |      |          | 8.6.1.4 Serial Clock Rate (SCR)                             |      |

|   |      | 8.6.2    | SSP Control Register 1                                      | 8–9  |

|   |      |          | 8.6.2.1 Receive FIFO Interrupt Mask (RIM)                   |      |

|   |      |          | 8.6.2.2 Transmit FIFO Interrupt Mask (TIM)                  |      |

|   |      |          | 8.6.2.3 Loop Back Mode (LBM)                                | 8–10 |

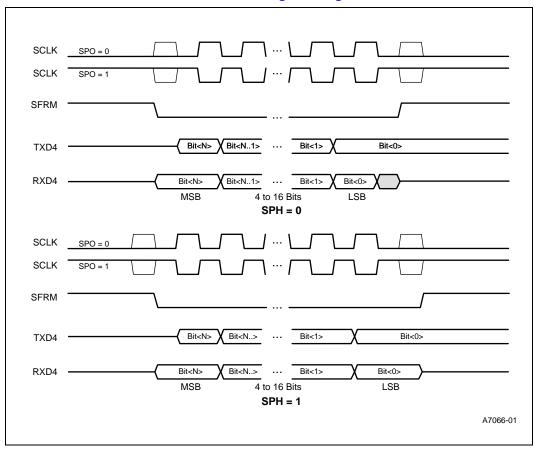

|   |      |          | 8.6.2.4 Serial Clock Polarity (SPO)                         |      |

|   |      |          | 8.6.2.5 Serial Clock Phase (SPH)                            | 8–10 |

|   |      |          | 8.6.2.6 Transmit FIFO Interrupt Threshold (TFT)             | 8–11 |

|   |      |          | 8.6.2.7 Receive FIFO Interrupt Threshold (RFT)              | 8–11 |

|   |      | 8.6.3    | SSP Data Register (SSPDR)                                   |      |

|   |      | 8.6.4    | SSP Status Register                                         | 8–13 |

|   |      |          | 8.6.4.1 Transmit FIFO Not Full Flag (TNF) read-only,        |      |

|   |      |          | non-interruptible)                                          | 8–13 |

|   |      |          | 8.6.4.2 Receive FIFO Not Empty Flag (RNE) read-only,        |      |

|   |      |          | non-interruptible)                                          |      |

|   |      |          | 8.6.4.3 SSP Busy Flag (BSY) read-only, non-interruptible)   | 8–14 |

|   |      |          | 8.6.4.4 Transmit FIFO Service Request Flag (TFS) read-only, |      |

|   |      |          | maskable interrupt)                                         | 8–14 |

|   |      |          | 8.6.4.5 Receive FIFO Service Request Flag (RFS) read-only,  |      |

|   |      |          | maskable interrupt)                                         | 8–14 |

|   |      |          | 8.6.4.6 Receiver Overrun Status (ROR) (read/write,          |      |

|   |      |          | non-maskable interrupt)                                     | 8–14 |

|   |      |          | 8.6.4.7 Transmit FIFO Level                                 |      |

|   |      | 0.0.5    | 8.6.4.8 Receive FIFO Level                                  |      |

|   |      | 8.6.5    | SSP Interrupt Test Register (SSPITR)                        |      |

|   |      | 8.6.6    | SSP Register Address Map                                    | 8–16 |

| 9 | PS/2 | Trackp   | oad and Mouse Interfaces                                    | 9–1  |

|   |      | -        |                                                             |      |

|   | 9.1  | •        | Prs                                                         |      |

|   |      | 9.1.1    | Control Register (KBDCR)                                    |      |

|   |      | 9.1.2    | Status Register (KBDSTAT)                                   |      |

|   |      | 9.1.3    | Transmit/Receive Data Register (KBDDATA)                    |      |

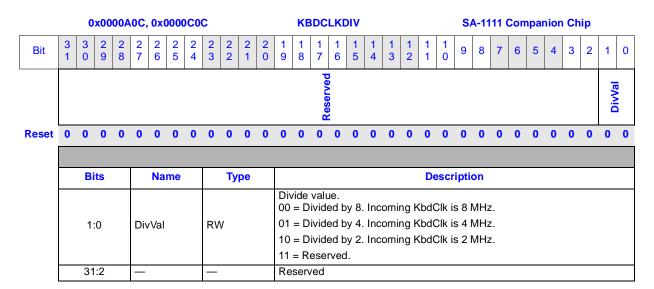

|   |      | 9.1.4    | Clock Division Register (KBDCLKDIV)                         |      |

|   |      | 9.1.5    | Clock Precount Register (KBDPRECNT)<8>                      |      |

|   |      | 9.1.6    | KBD Interrupt Test Register (KBDITR)                        |      |

|   |      | 9.1.7    | Register Memory Map                                         |      |

|   | 9.2  | Function | onal Description                                            | 9–6  |

|   |      |          |                                                             |      |

# int<sub>el®</sub>

| 10 | Gene  | eral-Purpose I/O Interface                         | 10–1  |

|----|-------|----------------------------------------------------|-------|

|    | 10.1  | Functional Description                             | 10–1  |

|    | 10.2  | GPIO Pin List and Description                      | 10–2  |

|    | 10.3  | Programmer's Model                                 |       |

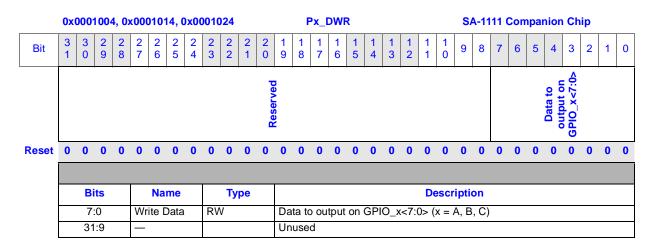

|    |       | 10.3.1 Data Value Register (Px_DWR - Write)        |       |

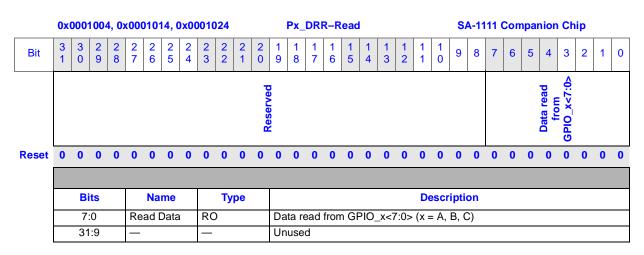

|    |       | 10.3.2 Data Value Register (Px_DRR - Read)         |       |

|    |       | 10.3.3 Data Direction Register (Px_DDR)            |       |

|    |       | 10.3.4 Sleep State Register (Px_SSR)               |       |

|    |       | 10.3.5 Sleep Direction Register (Px_SDR)           |       |

|    |       | 10.3.6 Memory Map                                  |       |

|    | 10.4  | Test                                               | 10–6  |

| 11 | Inter | rupt Controller                                    | 11–1  |

|    | 11.1  | Functional Description                             |       |

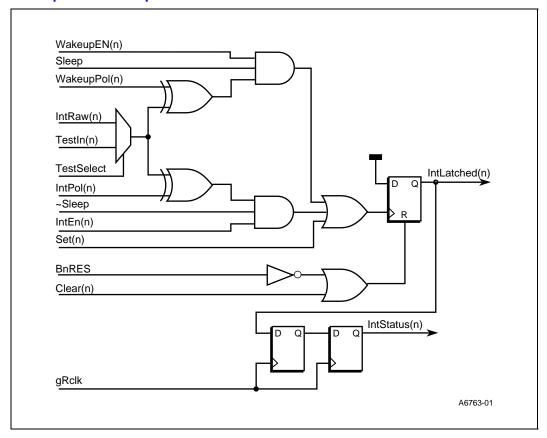

|    |       | 11.1.1 Logic Diagrams                              |       |

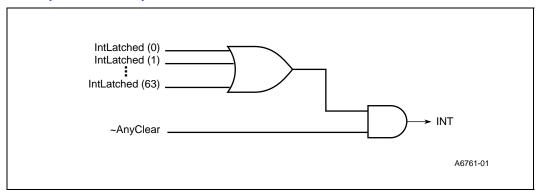

|    |       | 11.1.2 Application                                 |       |

|    | 11.2  | Interrupt Sources                                  |       |

|    | 11.3  | Interrupts                                         |       |

|    |       | 11.3.1 GPIO Interrupts                             |       |

|    |       | 11.3.2 Wake-Up Interrupts                          |       |

|    |       | 11.3.3 Multiple Interrupts                         |       |

|    | 11.4  | Testability                                        |       |

|    | 11.5  | Programmer's Model                                 |       |

|    |       | 11.5.1 Registers                                   |       |

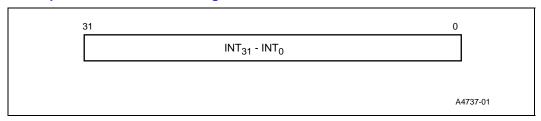

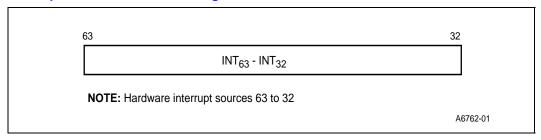

|    |       | 11.5.1.1Source Bit Positions                       |       |

|    |       | 11.5.2 INTTEST0 – INTTEST1                         |       |

|    |       | 11.5.3 INTENO – INTEN1                             |       |

|    |       | 11.5.4 INTPOL0 – INTPOL1                           |       |

|    |       | 11.5.5 INTTSTSEL                                   |       |

|    |       | 11.5.6 INTSTATCLR0–1                               |       |

|    |       | 11.5.7 INTSET0 – INTSET1                           |       |

|    |       | 11.5.8 WAKE_EN0 - WAKE_EN1                         |       |

|    |       | 11.5.9 WAKE_POL0 - WAKE_POL1                       |       |

|    | 11.6  | 11.5.10 Memory Map Characteristics                 |       |

|    |       |                                                    |       |

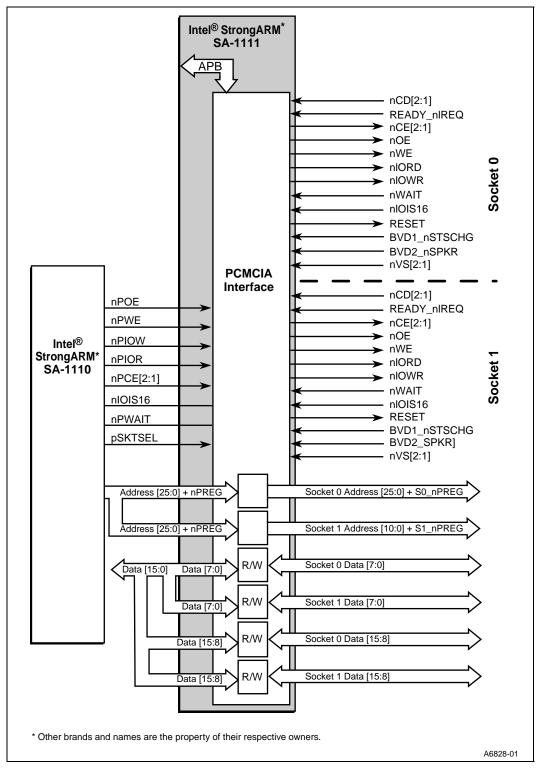

| 12 | PCM   | CIA Interface                                      |       |

|    | 12.1  | PCMCIA Interface Block Diagram                     |       |

|    | 12.2  | Functional Description                             | 12–3  |

|    |       | 12.2.1 PCMCIA/CF Address and Data Buffers          |       |

|    |       | 12.2.2 Voltage Control                             | 12–3  |

|    |       | 12.2.3 Reset Signals                               |       |

|    |       | 12.2.4 Control Signals                             |       |

|    |       | 12.2.5 Interrupts                                  |       |

|    | 12.3  | Detailed Signal Descriptions                       |       |

|    | 40.4  | 12.3.1 Intel® StrongARM* SA-1111 Interface Signals |       |

|    | 12.4  | Socket 0 Signals                                   |       |

|    | 12.5  | Socket 1 Signals                                   |       |

|    | 12.6  | Programmer's Model                                 |       |

|    |       | 12.6.1 Status Register (PCSR)                      |       |

|    |       | 12.6.2 Control Register (PCCR)                     | 12–12 |

# int<sub>el®</sub>

|         |            | 12.6.3 Sleep State Register (PCSSR)                             |        |

|---------|------------|-----------------------------------------------------------------|--------|

|         |            | 12.6.4 Memory Map                                               | 12–13  |

| 13      | Elec       | trical and Timing Specifications                                | 13–1   |

|         | 13.1       | AC and DC Signal Requirements                                   |        |

|         | 13.2       | DC Specifications                                               | 13–2   |

|         |            | 13.2.1 Power Supply Voltages                                    |        |

|         |            | 13.2.2 Absolute Maximum Ratings                                 |        |

|         |            | 13.2.3 CMOS Input Voltage Levels                                |        |

|         |            | 13.2.4 DC Operating Conditions                                  |        |

|         |            | 13.2.5 Compact Flash and PCMCIA 4mA Buffer Input Voltage Levels | s 13–4 |

|         | 13.3       | AC Characteristics                                              |        |

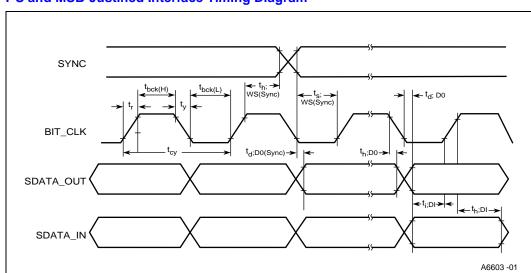

|         |            | 13.3.1 I2S and MSB-Justified Interface Timing                   |        |

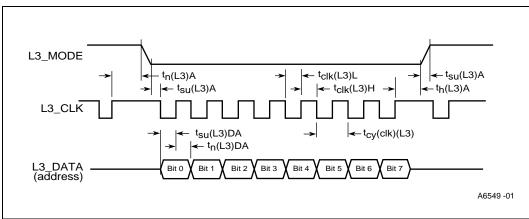

|         |            | 13.3.2 L3 Control Bus Interface Timing                          |        |

|         |            | 13.3.3 AC-link Interface Timing                                 | 13–8   |

| 14      | Pack       | rage and Pinout                                                 | 14–1   |

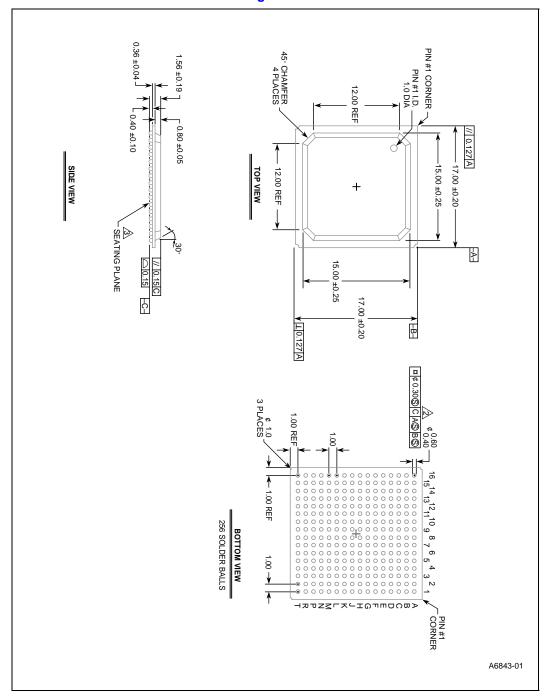

|         | 14.1       | Package                                                         | 14–1   |

| Figures |            |                                                                 |        |

|         | 4.4        | Oustana Black Diagnam                                           | 4.0    |

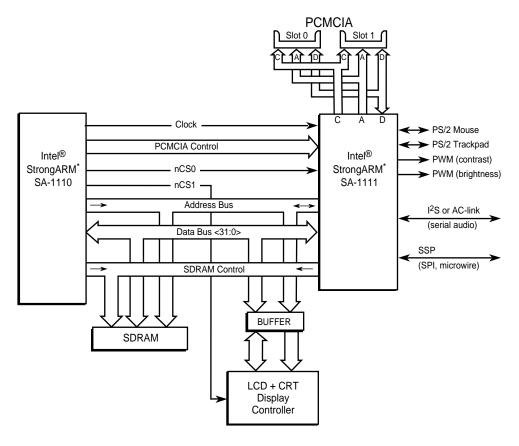

|         | 1-1        | System Block Diagram                                            |        |

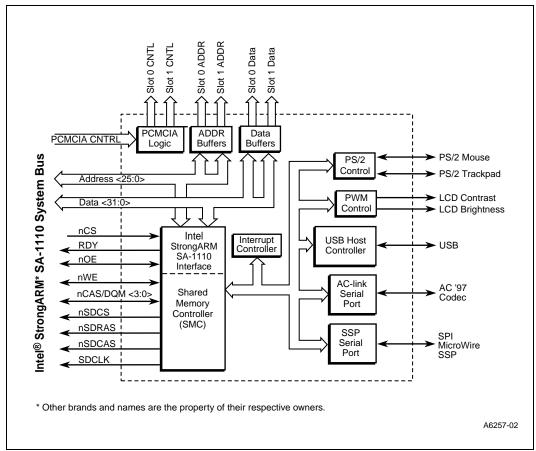

|         | 2-1        | SA-1111 Block Diagram                                           |        |

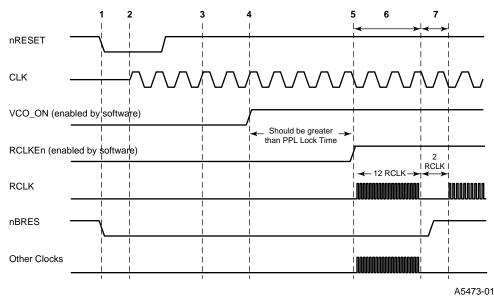

|         | 2-2<br>3-1 | SA-1111 Reset Sequence                                          |        |

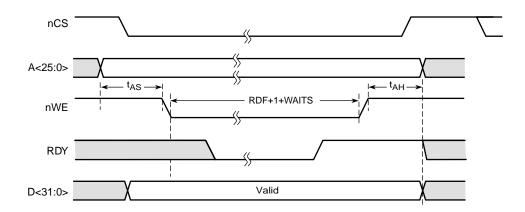

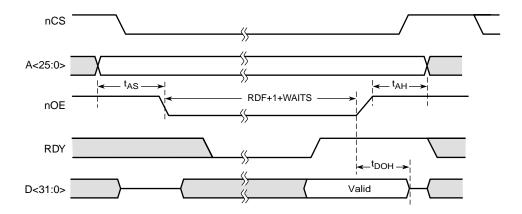

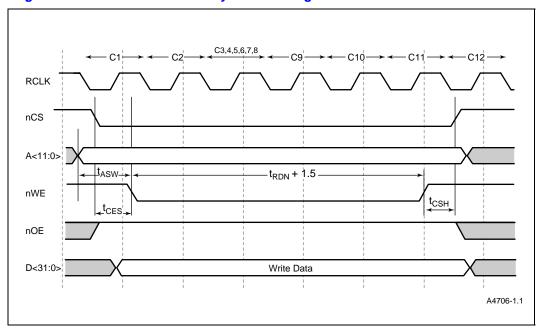

|         | 3-1<br>3-2 | Register Write, Single Cycle with Variable Latency              |        |

|         | 3-2<br>3-3 | Register Read, Single Cycle with Variable Latency               |        |

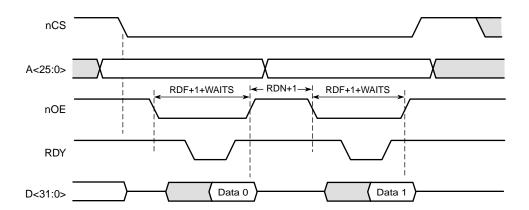

|         | 3-4        | Register Write, Burst of 2 with Variable Latency                |        |

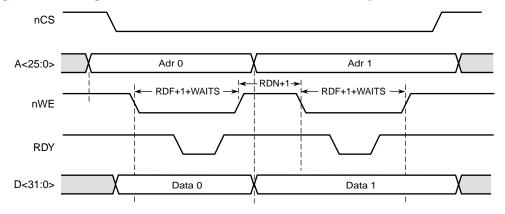

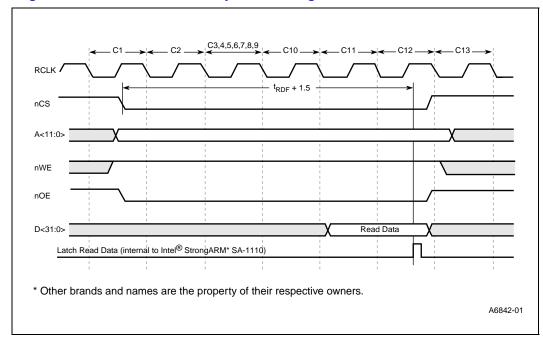

|         | 3-5        | Register Reads with Fixed Latency Mode of Register Access       |        |

|         | 3-6        | Register Writes with Fixed Latency Mode of Register Access      |        |

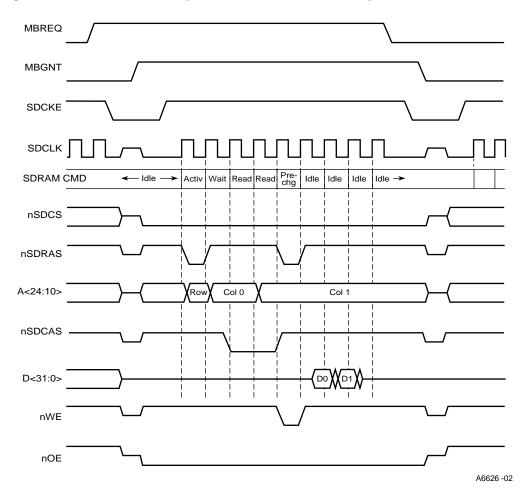

|         | 3-7        | SDRAM Read Cycle, Burst of 2 - CAS Latency = 3                  |        |

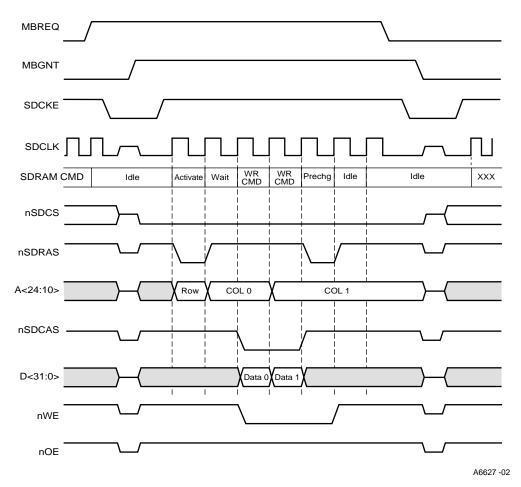

|         | 3-8        | SDRAM Write Cycle, Burst of 2                                   |        |

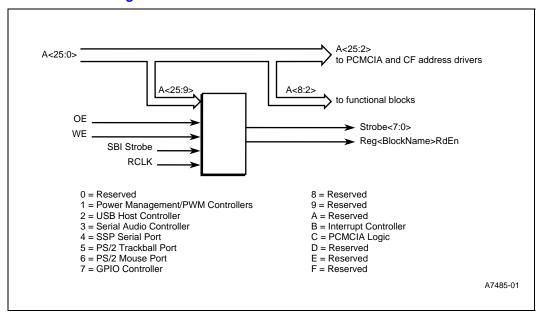

|         | 4-1        | Decoder Block Diagram                                           |        |

|         | 4-2        | Arbiter Block Diagram                                           |        |

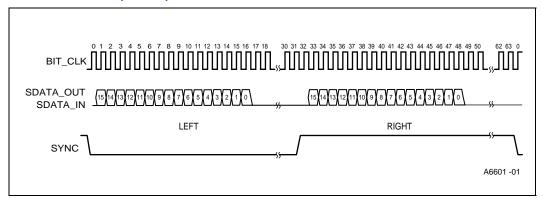

|         | 7-1        | AC-Link Audio Output Frame                                      |        |

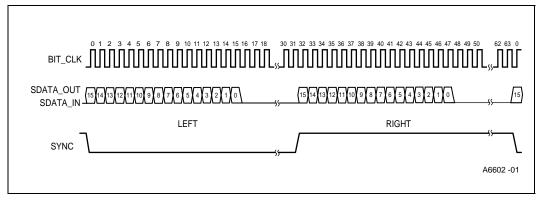

|         | 7-2        | AC-Link Audio Input Frame                                       |        |

|         | 7-3        | I2S Data Formats (16 bits)                                      |        |

|         | 7-4        | MSB-Justified Data Formats (16 bits)                            |        |

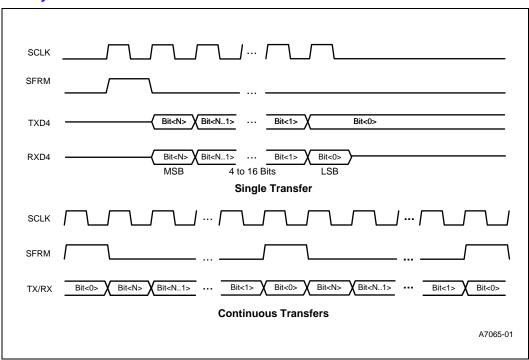

|         | 8-1        | SSP Synchronous Serial Frame Format                             |        |

|         | 8-2        | SPI Frame Format                                                |        |

|         | 8-3        | National Microwire* Frame Format                                | 8–6    |

|         | 8-4        | Clock Phase Formats for SPO and SPH Programming                 | 8–11   |

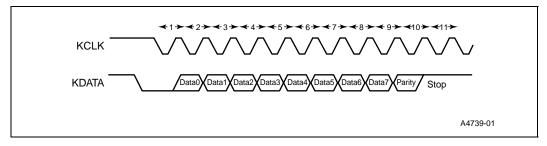

|         | 9-1        | Keyboard/Mouse Controller Receive Protocol                      |        |

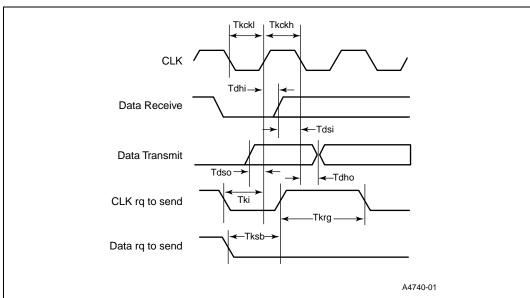

|         | 9-2        | Timing and Controller Request to Send Protocol                  |        |

|         | 11-1       | Interrupt and Wake-Up Generation                                |        |

|         | 11-2       | Interrupt and Wake-Up Combination                               |        |

|         | 11-3       | Interrupt Source Positions in Register Set 0                    |        |

|         | 11-4       | Interrupt Source Positions in Register Set 1                    | 11–6   |

|         | 12-1       | PCMCIA Interface Block Diagram                                  |        |

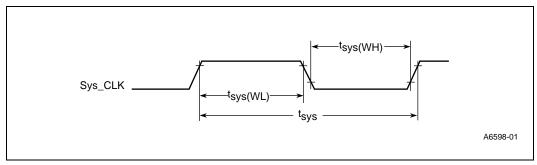

|         | 13-1       | I2S and MSB-Justified SYS_CLK Timing Diagram                    |        |

|         | 13-2       | I2S and MSB-Justified Interface Timing Diagram                  | 13–6   |

# int<sub>e</sub>l<sub>®</sub>

**Tables**

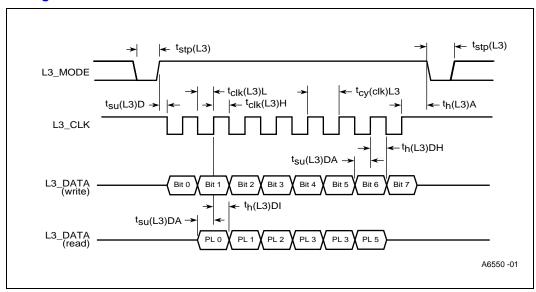

| 13-3 | Timing for L3 Address Mode                                               | 13–7    |

|------|--------------------------------------------------------------------------|---------|

| 13-4 | Timing for L3 Data Transfer Mode                                         | 13–7    |

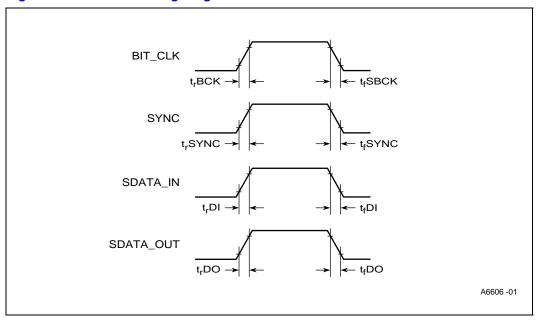

| 13-5 | Signal Rise and Fall Timing Diagram                                      | 13–8    |

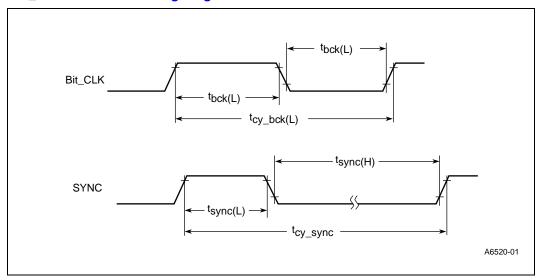

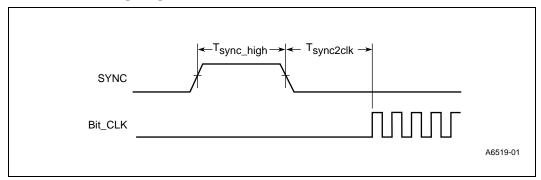

| 13-6 | BIT_CLK and SYNC Timing Diagram                                          | 13–9    |

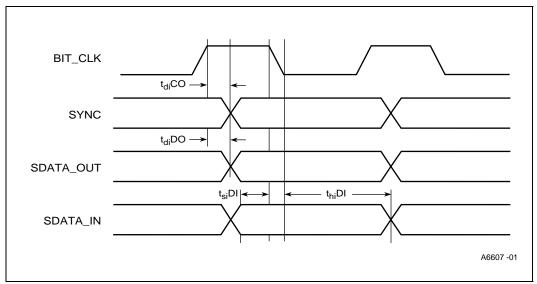

| 13-7 | Data Output and Input Timing Diagram                                     | . 13–10 |

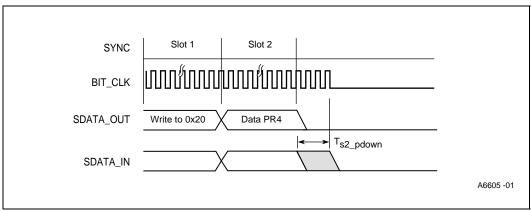

| 13-8 | AC-Link Low-Power Mode Timing Diagram                                    | .13–10  |

| 13-9 | Warm Reset Timing Diagram                                                | .13–11  |

| 14-1 | SA-1111 256 mBGA Mechanical Drawing                                      | 14–2    |

|      |                                                                          |         |

|      |                                                                          |         |

|      |                                                                          |         |

| 1-1  | Bit Definitions                                                          |         |

| 1-2  | Signal Descriptions                                                      |         |

| 2-1  | Pin State After Reset and During Sleep State                             |         |

| 2-2  | USB_PwrCntl Pin State in Sleep Mode                                      |         |

| 3-1  | SA-1110 Memory Interface Signals - O(D) = Driven for DMA                 |         |

| 3-2  | SBI Block - interface to DMA Bus (SBI is transfer target)                |         |

| 3-3  | SBI Block - interface to Register Access Bus (SBI is transfer initiator) |         |

| 3-4  | Other System Interface Signals                                           | 3–3     |

| 3-5  | SA-1111 Memory Map                                                       |         |

| 3-6  | Register Read and Write Timing Parameters - Variable Latency             |         |

| 3-7  | Register Read and Write Timing Parameters - RDY disabled                 | 3–9     |

| 3-8  | DRAM Address Configuration and Register Settings                         |         |

| 3-9  | SKCR Bit Descriptions                                                    | 3–15    |

| 3-10 | SMCR Bit Descriptions                                                    | 3–16    |

| 3-11 | SKID Bit Descriptions                                                    | 3–18    |

| 3-12 | SBI Memory Map                                                           | 3–18    |

| 4-1  | RAB Target Blocks/Address Assignment                                     |         |

| 4-2  | Register Access Bus Signal Description                                   | 4–3     |

| 4-3  | DMA Bus Interface Signals                                                | 4–4     |

| 4-4  | Arbiter Signals                                                          | 4–5     |

| 4-5  | Bus Master Priorities                                                    | 4–6     |

| 5-1  | SKPCR Bit Descriptions                                                   | 5–2     |

| 5-2  | SKCDR Bit Descriptions                                                   | 5–3     |

| 5-3  | SKAUD Bit Descriptions                                                   | 5–4     |

| 5-4  | Audio Sampling Frequencies                                               |         |

| 5-5  | SKPMC Bit Descriptions                                                   | 5–5     |

| 5-6  | SKPTC Bit Descriptions                                                   | 5–5     |

| 5-7  | SKPEN0 Bit Descriptions                                                  |         |

| 5-8  | SKPWM0 Bit Descriptions                                                  | 5–6     |

| 5-9  | SKPEN1 Bit Descriptions                                                  | 5–7     |

| 5-10 | SKPWM1 Bit Descriptions                                                  |         |

| 5-11 | System Controller - Read/Write Locations                                 |         |

| 6-1  | Operational Power Status                                                 |         |

| 6-2  | RAB Interface Signals                                                    |         |

| 6-3  | DMA Bus Interface Signals                                                |         |

| 6-4  | Status Register Bit Descriptions                                         |         |

| 6-5  | Interrupt Test Register Bit Descriptions                                 |         |

| 6-6  | Reset Register Bit Descriptions                                          |         |

| 6-7  | USB Host Interface Register Memory Map                                   |         |

| 7-1  | External Interface to Codec                                              | 7–2     |

# int<sub>el®</sub>

| 7-2          | L3 Bus Interface Pins                                       | 7–2  |

|--------------|-------------------------------------------------------------|------|

| 7-3          | RAB Interface Signals                                       | 7–3  |

| 7-4          | DMA Bus Interface Signals                                   | 7–3  |

| 7-5          | Other Signals                                               | 7–4  |

| 7-6          | Audio Sampling Frequency as a Function of PLL Divider Value | 7–6  |

| 7-7          | SACR0 Bit Descriptions                                      | 7–10 |

| 7-8          | SACR1 Bit Descriptions                                      |      |

| 7-9          | SACR2 Bit Descriptions                                      |      |

| 7-10         | SASR0 Bit Descriptions                                      |      |

| 7-11         | SASR1 Bit Descriptions                                      |      |

| 7-12         | SASCR Bit Descriptions                                      |      |

| 7-13         | L3CAR Bit Descriptions                                      |      |

| 7-14         | L3CDR Bit Descriptions                                      |      |

| 7-15         | ACCAR Bit Descriptions                                      |      |

| 7-16         | ACCDR Bit Descriptions                                      |      |

| 7-17         | ACSAR Bit Descriptions                                      |      |

| 7-17<br>7-18 | ACSDR Bit Descriptions                                      |      |

| 7-10<br>7-19 | SADTCS Bit Descriptions                                     |      |

| 7-19<br>7-20 | ·                                                           |      |

| 7-20<br>7-21 | SADTSA Bit Descriptions                                     |      |

|              | SADTCA Bit Descriptions                                     |      |

| 7-22         | SADTOR Bit Descriptions                                     |      |

| 7-23         | SADTCB Bit Descriptions                                     |      |

| 7-24         | SADRCS Bit Descriptions Bit Descriptions                    |      |

| 7-25         | SADRSA Bit Descriptions                                     |      |

| 7-26         | SADRCA Bit Descriptions                                     |      |

| 7-27         | SADRSB Bit Descriptions                                     |      |

| 7-28         | SADRCB Bit Descriptions                                     |      |

| 7-29         | SAITR Bit Descriptions                                      |      |

| 7-30         | SADR Bit Descriptions                                       |      |

| 7-31         | Serial Audio Controller Register Memory Map                 |      |

| 8-1          | External Interface to Codec                                 | 8–1  |

| 8-2          | RAB Interface Signals                                       | 8–2  |

| 8-3          | SSP Control Register 0 Bit Descriptions                     | 8–9  |

| 8-4          | SSP Control Register 1 Bit Descriptions                     | 8–12 |

| 8-5          | SSP Data Register Bit Descriptions                          | 8–13 |

| 8-6          | SSP Status Register Bit Descriptions                        | 8–15 |

| 8-7          | SSPITR Bit Descriptions                                     | 8–16 |

| 8-8          | SSP Register Address Map                                    | 8–16 |

| 9-1          | KBDCR Bit Descriptions                                      | 9–1  |

| 9-2          | KBDSTAT Bit Descriptions                                    |      |

| 9-3          | KBDDATA Bit Descriptions                                    |      |

| 9-4          | KBDCLKDIV Bit Descriptions                                  |      |

| 9-5          | KBDPRECNT Bit Descriptions                                  |      |

| 9-6          | KBDITR Bit Descriptions                                     |      |

| 9-7          | Trackpad Register Memory Map                                |      |

| 9-8          | Mouse Register Memory Map                                   |      |

| 9-9          | Keyboard/Mouse Interface Timings                            |      |

| 10-1         | GPIO Pin List                                               |      |

| 10-1         | Px_DWR Bit Descriptions                                     |      |

| 10-2         | Px_DRR-Read Bit Descriptions                                |      |

| 10-3         | ·                                                           |      |

| 10-4         | Px_DDR Bit Descriptions                                     | 10−4 |

# intel<sub>®</sub>

| 10-5  | Px_SSR Bit Descriptions                                        | 10–5  |

|-------|----------------------------------------------------------------|-------|

| 10-6  | Px_SDR Bit Descriptions                                        | 10–5  |

| 10-7  | GPIO Register Memory Map                                       | 10–6  |

| 11-1  | Interrupt Sources                                              | 11–3  |

| 11-2  | Interrupt Registers                                            | 11–8  |

| 11-3  | Interrupt Characteristics                                      | 11–8  |

| 12-1  | Interrupt Signals                                              | 12–4  |